作为曾经的日本半导体大牛股,Lasertec(6920 JP)的股价最近可谓是一波三折。先是几个月前做空机构发布看空公司的报告导致股价大跌,然后Lasertec在上一次法说会发布了强劲的业绩,有力地打脸了做空机构和一众做空该股票的对冲基金。不得不承认,Lasertec上一季度的业绩的确非常亮眼,特别是它的新增订单大幅增长,出乎大多数投资人的意料。但笔者在Lasertec的法说会上注意到非常有意思的一点:新任社长在回答一位卖方分析师的问题时讲到,目前公司的mask inspection tool order backlog当中,来自mask shop的订单比例和来自wafer fab的订单比例差不多是50:50。我们知道,从top down level的TAM来看的话,wafer fab用的mask inspection tool market size应该要比mask shop用的market size大很多,那Lasertec作为在EUV mask inspection tool市场的垄断型玩家,其order backlog中来自wafer fab的订单比例不应该比来自mask shop的订单比例高很多吗?为什么公司社长又说该比例是50:50呢?

要回答清楚这个问题,我们要对Lasertec所在的EUV mask inspection tool这个市场有一个全面的了解。首先,让我们来回顾一个最基础的问题:为什么现在的先进制程需要使用EUV光刻机?

我们知道,半导体光刻机是一个光学成像设备,其成像的分辨率极限(minimum critical dimension)遵循物理上的瑞利判据(Rayleigh criterion):

上述公式中,λ 是光刻机光源的波长,NA(numerical aperture)指的是光刻机中光学系统可以收集到的amount of light,K1是一个光学系数。下表列出了采用不同光源的光刻机系统的三种参数(λ/NA/K1)以及最后能够达到的成像分辨率极值(见CD or resolution一栏):

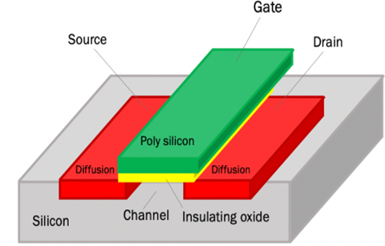

简单来说,一颗芯片是由无数个晶体管构成的,而一个晶体管是由源极、漏极、和栅极组成的。栅极控制了电流是否从源极流到漏极(见下图):

半导体制程上所谓的几纳米node原本指的是一颗芯片里面两个相邻的最小的晶体管之间的距离。当然,现在各家foundry 厂商的先进制程命名已经脱离了这一定义,而变成一种纯粹的名字符号了。下表列出了从7纳米制程往后各代先进制程的最小晶体管间距(见metal pitch一栏):

这里我们需要理解清楚一点:前文中光刻机根据瑞利判据所能成像的极限分辨率(CD min)约等于上表中给出的最小晶体管间距(min metal pitch)的一半。这是因为pitch size理论上来说衡量的是两个相邻的晶体管之间从中心线到中心线的距离(见下图),而CD则指的是光刻机可以在芯片上刻出的最小图案,即最小晶体管的栅极。在以前,当晶体管仍为2D结构时,其栅极的宽度约等于晶体管间距的一半,因此CD min = min metal pitch/2 就变成了行业里约定俗成的算法。当然现在在3D结构下晶体管栅极的宽度已经不是正好等于晶体管间距的一半了。

我们比较上文中的两张图表可知,浸没式ArF光刻机能够达到的最小CD为27.6nm,而7纳米制程的最小金属间距为40nm, 27.6 > 40/2, 因此从7纳米制程往后业界开始使用EUV光刻机。再往后则需要开始使用下一代的High NA EUV光刻机。所谓High NA EUV,是指光刻机设备所使用的光源不变,仍为13.5nm的极紫外线(EUV),但通过增强整个光学系统提高了numerical aperture (比如采用了更大的镜片,增大了光锥的开口等),从而提升了极限分辨率(CD min):

理论上来说从2纳米制程开始就应该要使用High NA EUV光刻机了(min metal pitch 22/2 = 11 = high NA EUV CD),但一方面ASML的High NA EUV在2025年还没有完全ready,另一方面2纳米制程有一个关键的晶体管结构转变(FinFET to GAA),因此业界不敢在2纳米制程同时采用两项技术变革(FinFET to GAA & Low NA to High NA EUV),而选择更安全稳妥的做法:即仍然使用low NA EUV, 但通过multiple patterning的方法来降低 K1系数从而达到更小的resolution。目前英特尔计划从A14制程(即1.4nm)开始正式采用High NA EUV,而台积电则更为保守,考虑从A10制程(即1nm)开始才正式采用High NA EUV。

理解了先进制程为什么要从DUV转到EUV光刻机,下一步我们还需要理解DUV photomask和EUV photomask的区别。 与穿透式(transmissive)的DUV photomask不同,EUV photomask是反射式的(reflective,见上图)。 简单来说,EUV photomask生产商要在掩模基板(substrate)上沉积40~50层钼和硅的反射层,反射层之上则还有一层吸收层(absorber),见下图。当进行曝光时,EUV light一层层地穿透EUV photomask, 每到一层就有一部分光被反射出去,当EUV photomask里所有层数的pattern全都被反射完之后,这些图案即共同组成了一个完整的photomask pattern,而patterned absorber则通过阻挡部分光的反射形成了掩膜上的dark features。

介绍完了DUV vs. EUV photomask,现在我们可以开始正式介绍photomask inspection equipment了。其实准确地来说,photomask inspection equipment属于semiconductor process control equipment中的一小类,其中又可以细分为mask blank inspection tool, patterned mask inspection tool, 以及mask defect review tool。Mask blank inspection顾名思义指的是对还未形成图案的mask blank进行检测。Mask inspection 指的是对整片已形成图案的photomask进行完整但较低分辨率地扫描,并快速定位出潜在的defect candidates。这些defect candidates然后被mask defect review tool以高分辨率进行放大检查(类似于被放在显微镜底下查看细节),最后mask shop会决定哪些defects较为严重需要进行修复。Photomask pattern的最大可接受的缺陷度一般为CD的10%。

Mask inspection tool又被分为mask shop用和wafer fab用tool。Mask shop采用die-to-database mask inspection tool,而wafer fab则一般采用die-to-die mask inspection tool。这里的区别在于:Die-to-die 通过将被检测芯片的图案与另一个作为黄金标准的reference芯片的图案相减,可以快速地检测到两者间微小的差别(即缺陷);而die-to-database则是将被检测芯片的图案与数据库中保存的理想图案相减。这种方法可以检测出两个芯片中存在的系统性缺陷,而这些缺陷无法通过die-to-die的方法识别。Mask shop因为需要保证出厂的photomask与设计图案完全一致,因此选择采用die-to-database tool来检测;而wafer fab因为更注重量产时的throughput,因此选择采用更快更省时的die-to-die tool(有时也需要辅以die-to-database)。

Lasertec目前拥有100% market share在EUV mask blank inspection tool和EUV mask inspection tool (both in mask shop & wafer fab),在DUV mask inspection tool则是和KLA Tencor均分市场。Zeiss则是在EUV mask defect review tool拥有100% market share。

EUV photomask与DUV photomask相比最难检测的一点在于phase shift defect。所谓phase shift defect是指那些隐藏在几十层反射层之间的defect(DUV mask没有这样的multilayer结构),这些缺陷会破坏反射层图案的间距,并在EUV light被反射时导致光的相移。只有 EUV 光源才能够检测到 EUV photomask里多层结构中深藏的缺陷,而其他波长的光源则只能看到photomask表面的几层(见下图,最左侧为13.5nm的EUV光波长)。

而未来的High NA EUV又会需要新的技术进步来进行photomask检测。High NA EUV与Low NA EUV检测的两个主要差别是:1)High NA EUV的缺陷更加小了,因此检测机台的灵敏度(信噪比)必须提高;2)High NA EUV的光学系统有所改变。具体来说,要达到更高的numerical aperture就意味着要采用更大的镜子,但更大的镜子也意味着EUV光线照射到photomask的入射角也会变得更大,而更大的入射角会大幅降低photomask的反射率(例:想象一束光线从近乎水平的角度照射到一个平面物体上vs.这束光线从45度角照射该物体的反射率差别),导致photomask pattern无法被光刻机print到wafer上。这个问题可以通过将图案缩小 8 倍而不是low NA EUV中使用的 4 倍来解决,但这又需要改用更大的photomask,导致整个photomask相关的ecosystem 进行redesign。最后为了避免引起整个supply chain redesign的麻烦,ASML选择了保持photomask size不变而改变自己的光学系统:即High NA EUV的镜子不是均匀地缩小要打印的图案by 4倍,而是在X轴方向上将其缩小 4 倍,在Y轴方向上将其缩小 8 倍。这样的变形光学设计所形成的椭圆形光锥既有效降低了光线照射到photomask的入射角度,也避免了入射光锥与反射光锥相互重叠的问题(见下图)。

当然,这样的变形光学设计又引起了另一个问题:half field exposure,即High NA EUV单次曝光的field size只有原本Low NA EUV的一半(因为Y轴的长度只有原来的一半)。这意味着对相同的wafer进行光刻,High NA EUV需要原本Low NA EUV两倍的曝光次数。为了解决这一问题,ASML提升了其stages的移动速度(wafer stage提升2x,reticle stage提升4x),从而保证了整台High NA EUV光刻机的wafer throughput即便在单片wafer曝光次数需要翻倍的情况下也能达到和原本Low NA EUV一样。

回到Lasertec,下面介绍一下公司的几大旗舰产品机台:

MAGICS series – DUV mask blank inspection tool

MATRICS series – DUV mask inspection tool

ABICS series – EUV mask blank inspection tool

ACTIS series – EUV mask inspection tool (for wafer fab use)

MIAS series – EUV mask inspection tool (for mask shop use)

根据笔者的了解,目前Lasertec的EUV mask inspection tool installed base大致为:英特尔14台,台积电9台,三星3台;其EUV mask blank inspection tool installed base大致为9台。

后文笔者会进一步介绍不同的EUV光源类型,Lasertec所面临的竞争问题(vs. KLA & Zeiss),以及Lasertec接下来的订单情况。