在之前的文章里(The Bonder War – An update on ASMPT (522 HK),BESI (BESI NA), Shibaura (6590 JP), Tazmo (6266 JP) and other advanced packaging equipment players)笔者详细介绍了台积电目前CoWoS工艺制程当中用到的各种键合(bonding)设备。但我们知道台积电对太先进的技术一直抱持着相对保守谨慎的态度,宁愿让竞争对手先上,等到该技术相对成熟了自己再开始采用(不愿意做第一个吃螃蟹的人,避免踩坑)。这在前道工艺中体现在了GAA(三星率先量产,台积要等到2026年才大规模量产)和High NA EUV (Intel率先采购,台积目前规划要等到2030年之后才上量产);而在后道工艺中则体现在了台积的CoWoS制程至今都只是采用传统的flip chip bonding,而非更加先进的thermal compression bonding (Intel已大规模采用TCB)和hybrid bonding技术。因此,上一篇讲CoWoS的文章中只是抛砖引玉地轻轻提到了一下hybrid bonding,笔者将会在今天这一篇文章里对此做更详尽的介绍。

混合键合(英文名hybrid bonding)被业界认为是目前先进封装制程中最先进的技术,因为理论上它完全摆脱了芯片堆叠之间的micro-bump,用铜与铜互联(即via之间用一层极薄的copper pad连接而非球形的bump)达到了芯片之间的直接互联,极大地提高了芯片间信号传输的速度。而提到混合键合,就不免要提到BESI这家在欧洲上市的半导体设备公司 -- 由于BESI在混合键合设备中占据了近乎垄断的地位,最近一年来市场对先进封装的热忱把它家的股价直接送上了天。。。Street上对混合键合以及BESI的研究报告已经多如牛毛,因此笔者今天想另辟蹊径,从应用面的角度按客户按产品别的仔细拆解一下这个混合键合设备究竟用在哪些地方。

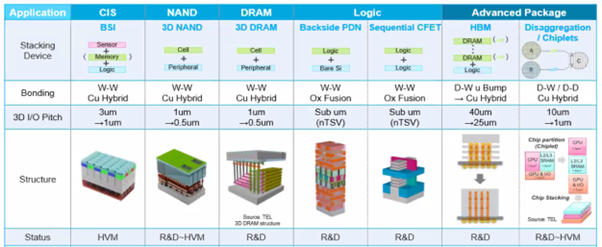

首先,让我们从top-down的角度系统性的梳理一下目前有哪些applications会用到混合键合(见下图):

上表对hybrid bonding的应用类别做了一个很好的概括(注:图中第三行中的fusion bonding指的也是hybrid bonding)。但需要注意的是,混合键合其实又分为W2W (wafer-to-wafer)和 D2W (die-to-wafer)两种类型。上表中浅蓝色的部分(即从CIS开始往右一直到logic BPDN/CFET)采用的都是W2W bonding;而深蓝色的advanced package部分采用的则是D2W bonding。我们平时所说的BESI在hybrid bonder市场拥有垄断地位,其实准确来说指的是它在D2W bonding市场拥有垄断地位;欧洲的另一家半导体设备公司EV Group则是在W2W bonding市场拥有垄断地位。

简单来说,W2W bonding顾名思义即是在wafer level直接把需要上下堆叠的两种晶片的晶圆bond在一起,最后再进行切割(dicing) vs. D2W bonding则是先切割好第一种晶片的晶圆,再用pick & place的方法把该晶片的KGD (known good die)bond到第二种晶片的晶圆上。W2W的优势在于成本低,throughput高。但W2W的缺点也非常明显:由于它是拿两片wafer直接做bonding,那该方法就只适用于上下两种晶片尺寸完全一样的情况(上下晶片尺寸不同就对不上);Wafer level bonding的另一个问题是无法提前sort出KGD,因此如果上下两种晶片中一种或两种晶片的生产良率都很低,那做W2W bonding的整体良率就会非常差(即一颗好的die被bond在另一颗不好的die上面,那这一组bonded dies就都废了)。所以我们看到,在logic用的advanced packaging制程上业界一般都采用D2W bonding(先进行KGD sorting),因为报废一整组packaged dies的成本实在是太高了;此外,W2W bonding对其bond的wafer也有一定的厚度要求(即不能太薄),这一点笔者会在后面讨论HBM4 hybrid bonding的时候展开讲一下。

接下来上重头戏,笔者将会按照BESI official presentation materials里面列出的时间线,为大家详细拆解一下它家的D2W混合键合设备到底用在了哪些晶片上。